# MARUDHAR KESARI JAIN COLLEGE FOR WOMEN, VANIYAMBADI PG & RESEARCH DEPARTMENT OF PHYSICS

#### **E-NOTES**

### **CLASS : II MSC PHYSICS**

### SUBJECT: MICROPROCESSOR (8085) & MICROCONTROLLER (8051) SUBJECT CODE: GPH33

### **SYLLABUS**

#### **Unit-3: Basic of Microcontroller 8051**

8051 Micro-controller hardware: 8051 oscillator and clock - Program counter and data pointer - A and B CPU register - Flags and PSW - Internal memory - Internal RAM - Stack and stack pointer - Special function registers - Internal ROM-Input / output pin, ports and circuits - External memory.

Counter and Timer: Counter / Timer interrupts - Timing - Timer modes of operation – Counting-Serial data input / Output: Serial data interrupt - Data transmission - Data reception - serial data transmission modes.

gram generated.

# 1.3 Four-Bit to Thirty-Two-Bit Microcontrollers

Every application demands a microcontroller that offers the right amount of functionality at the minimum cost. Applications vary from controlling an appliance to controlling an automobile. No single microcontroller design can economically meet these demands, so semiconductor manufacturers offer an array of microcontrollers designed to handle data in 4-, 8-, 16- and 32-bit words.

Bits are not the only thing that increase as word length grows. Additional functions are also added to meet market needs. Some of the more popular additional functions are

Analog-to-digital (A/D) converters, which change external analog signals to digital bits

Counter arrays, used to count and generate pulses

Watchdog timers (WDTs), which reset the controller if program execution hangs up

Serial data, both asynchronous (UART) and synchronous

Pulse width modulation (PWM). used. among other things. for motor speed control

Phase-locked-loops (PLLs), used for synchronous communications

External bus controllers for static (RAM/ROM) and dynamic (SDRAM) memories

If the market is large enough, say for automotive dashboard control and display, a high-end microcontroller will be designed and marketed by numerous companies just to meet that single application.

# Four-Bit Microcontrollers

In terms of sheer volume, 4-bit microcontrollers may be used more than any other type. For a commodity microcontroller, cost depends as much on the volume of the package and the number of pins as on the amount of silicon inside. Pin count, in turn, depends on the number of data bits commonly handled by the microcontroller, and its I/O capability. Using 4 bits reduces package cost and pin count to a minimum. Employed in applications ranging from alphanumeric LED/LCD display drivers to portable battery chargers, these are the least expensive "smart chips" available. An example of a contemporary 4-bit microcontroller is the Renasas M34501, in a 20-pin DIP:

| 4-bit RAM | 10-bit ROM | Counters | I/O Pins | Other Features |

|-----------|------------|----------|----------|----------------|

| 256       | 4K         | 2        | 14       | A/D, WDT       |

# **Eight-Bit Microcontrollers**

Eigh bit microcontrollers are perhaps the most popular microcontrollers in use today, judging from the number of semiconductor companies making them.

Eight bits have proven to be a very useful word size for everyday controller tasks. Capable of 256 decimal values, or quarter-percent resolution, the 1-byte data word is adequate for many control and monitoring applications. Serial ASCII code is also byte size, making 8 bits the natural choice for data communication applications. In addition, most low-cost RAM and ROM memories store 1 byte per memory location for easy interfacing to an 8-bit microcontroller.

One indication of the popularity of 8-bit microcontrollers is the fact that some 44 manufacturers produce over 600 models based on the 8051 architecture alone! Other popular microcontrollers, such as those designed by Microchip, Motorola, and Zilog, add hundreds of additional choices to the 8-bit menu. Here is what the 8051 offers when mounted in a 40-pin DIP:

| ROM       | ROM | Counters | I/O Pins | Other Features |

|-----------|-----|----------|----------|----------------|

| 128 bytes | 4K  | 2        | 32       | UART           |

Variations on a design occur when manufacturers offer models that include application-specific extras such as A/D and D/A converters, counter arrays, UARTs, WDT, and different memory configurations. On-chip ROM memory size may be increased, or ROMless models made that use off chip EPROMs for prototyping purposes. Flash and EEPROM memories may also be incorporated into the design.

# Sixteen-Bit Microcontrollers

Sixteen-bit microcontrollers offer much of the generality of 8-bit models, but with greatly increased memory size and speed. Sixteen-bit microcontrollers are also much better suited for programming in high-level languages, such as C.

Applications for 16-bit microcontrollers are calculation and data intensive and include disk drives, modems, printers, scanners, pattern recognition, and automotive and servomotor control. A typical 16-bit microcontroller, the Motorola 68HC16Z3, has these attributes when mounted in a 144-lead LQFP package:

| RAM | ROM | Counters |    | Other Features                |

|-----|-----|----------|----|-------------------------------|

|     |     | •        | 04 | Counter Array, UART, A/D, WDT |

| 4K  | 8K  | 2        | 24 | Counter Anay, Or a constant   |

## Thirty-Two-Bit Microcontrollers

Thirty-two-bit microcontrollers are currently evolving away from generalpurpose applications to targeted markets such as PDAs, GPS, automotive control, communication networks, robotics, entertainment/game boxes, digital cameras, cell phones, and similar high-end uses. As an example, the Sharp LH79520 housed in a 176-pin LQFP package offers the following features, most of which could be used to implement a notebook computer: 32K RAM, color LCD controller, three UARTs, synchronous serial, two PWMs, 64 I/O pins, four counters, WDT, real-time clock, PLL, and direct memory access (DMA). Clearly, the development of 32-bit microcontrollers is driven by large, well-defined markets, and must be studied on an individual basis.

#### 4 **Development Systems for Microcontrollers**

What is needed to be able to apply a microcontroller to your product? That is, what package of hardware and software will allow the microcontroller to be programmed and connected to your application? A package commonly called a development system is required.

First, trained personnel must be available either on your technical staff or as consultants. One person who is versed in digital hardware and computer software is the minimum number.

Second, a device capable of programming EPROMs must be available to test the prototype device. Many of the microcontroller families discussed have a ROMless version, an EPROM version, or an electrically erasable and programmable read only memory (EEPROM) version that lets the designer debug the hardware and software prototype before committing to full-scale production. Many inexpensive EPROM programmers are sold that plug into a port of most popular personal computers. More expensive, and more versatile, dedicated programmers are also available. An alternative to EPROMs are vendor-supplied prototype cards that allow code to be downloaded from a host computer and the program run from RAM for debugging purposes. An EPROM will eventu-

ally have to be programmed for the production version of the microcontroller. Finally, software is needed, along with a personal computer to host it. The minimum software package consists of a machine-language assembler, which can be supplied by the microcontroller vendor or bought from independent de

#### ORIFCIIACO

| On successful completion of this chapter you will be a | ble to | 0 | ): |  | 1 | 3 |  | ŝ |  |  |  |  | 1 | ł | t |  | 1 | ( | ( | C | C |  | C | ( | ( | ( | ( | ( | ( | ( | ( | 1 | 1 | 1 | 1 | ( | ( | ( | C |  | ) | ) | ) |  | C | C | ( | 1 | l | t | t | t | ł | t | t | t | t | t | t | t | t | t | t | t | t | 1 |  |  |  |  |  |  |  |  |  |  |  | ŝ | ŝ | į. | į. |  |  | į. | į. | į. | l | 8 | į. | ŝ | į. | į. | į. | l | ŝ | ŝ | ŝ | į. |  | l | l | l | , | 1 | 1 | 1 | Q | ę | ł | ( | 1 |  |  | ) |  | ł | 1 |  |  | 0 | )( | ł |  |  | l | i |  | V | ٨ | ١ |  | ۱ | U | 1 | ) | ¢ | ( | 1 | y | 1 |  | 1 | 1 | ( | 1 | 1 |

|--------------------------------------------------------|--------|---|----|--|---|---|--|---|--|--|--|--|---|---|---|--|---|---|---|---|---|--|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|--|---|---|---|--|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|--|--|--|--|--|--|--|--|--|--|--|---|---|----|----|--|--|----|----|----|---|---|----|---|----|----|----|---|---|---|---|----|--|---|---|---|---|---|---|---|---|---|---|---|---|--|--|---|--|---|---|--|--|---|----|---|--|--|---|---|--|---|---|---|--|---|---|---|---|---|---|---|---|---|--|---|---|---|---|---|

|--------------------------------------------------------|--------|---|----|--|---|---|--|---|--|--|--|--|---|---|---|--|---|---|---|---|---|--|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|--|---|---|---|--|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|--|--|--|--|--|--|--|--|--|--|--|---|---|----|----|--|--|----|----|----|---|---|----|---|----|----|----|---|---|---|---|----|--|---|---|---|---|---|---|---|---|---|---|---|---|--|--|---|--|---|---|--|--|---|----|---|--|--|---|---|--|---|---|---|--|---|---|---|---|---|---|---|---|---|--|---|---|---|---|---|

- Describe the hardware features of the 8051 microcontroller.

- List the internal registers of the 8051 microcontroller and their functions.

- Draw the machine cycle for the 8051 microcontroller.

- State the physical differences between the Port 0, 1, 2, and 3 I/O pins.

- Describe the various operating modes of the timer/counters and associated control registers.

- Describe the various operating modes of the UART, and associated control registers.

- List the types of interrupts, the interrupt program addresses, and the interrupt control registers.

#### 0 Introduction

The first task faced when learning to use a new computer is to become familiar with the capability of the machine. The features of the computer are best learned by studying the internal hardware design, also called the architecture of the device, to determine the type, number, and size of the registers and other circuitry.

The hardware is manipulated by an accompanying set of program instructions, or software, which is usually studied next. Once familiar with the hardware and software, the system designer can then apply the microcontroller to the problems at hand.

A natural question during this process is "What do I do with all this stuff?" Similar to attempting to write a poem in a foreign language before you have a vocabulary and rules of grammar, writing meaningful programs is not possible until you have become acquainted with both the hardware and the software of

This chapter provides a broad overview of the architecture of the 8051. In subsequent chapters, we will cover in greater detail the interaction between the

## 1 8051 Microcontroller Hardware

The 8051 microcontroller generic part number actually includes a whole family of microcontrollers that have numbers ranging from 8031 to 8751 and are available in N-Channel Metal Oxide Silicon (NMOS) and Complementary Metal Oxide

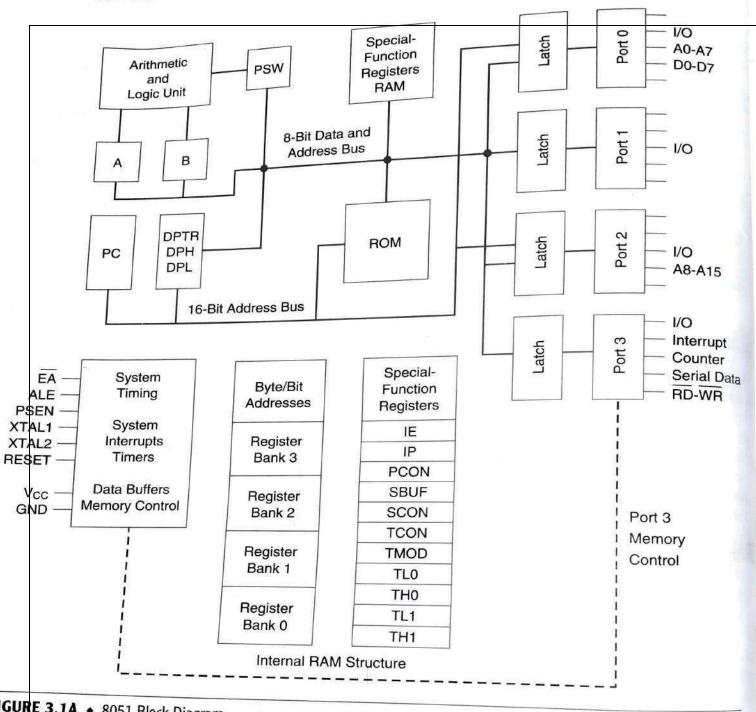

architecture. This galaxy of parts, the result of desires by the manufacturers to leave no market niche unfilled, would require many chapters to cover. In this chapter, we will study a "generic" 8051, housed in a 40-pin DIP, and direct the investigation of a particular type to the data books. The block diagram of the 8051 in Figure 3.1a shows all of the features unique to microcontrollers:

Internal ROM and RAM I/O ports with programmable pins Timers and counters Serial data communication

The figure also shows the usual CPU components: program counter, ALU, working registers, and clock circuits.<sup>1</sup>

The 8051 architecture consists of these specific features:

- Eight-bit CPU with registers A (the accumulator) and B

- Sixteen-bit program counter (PC) and data pointer (DPTR)

- Eight-bit program status word (PSW)

- Eight-bit stack pointer (SP)

- Internal ROM or EPROM (8751) of 0 (8031) to 4K (8051)

- Internal RAM of 128 bytes:

- Four register banks, each containing eight registers

- Sixteen bytes, which may be addressed at the bit level

- Eighty bytes of general-purpose data memory

- ◆ Thirty-two input /output pins arranged as four 8-bit ports: P0 P3

- Two 16-bit timer/counters: T0 and T1

- Full duplex serial data receiver/transmitter: SBUF

- · Control registers: TCON, TMOD, SCON, PCON, IP, and IE

- Two external and three internal interrupt sources

- Oscillator and clock circuits

<sup>1</sup>Knowledge of the details of circuit operation that cannot be affected by any instruction or external data, although intellectually stimulating, tends to confuse the student new to the 8051. For this reason, this text concentrates on the essential features of the 8051; the more advanced student may wish to refer to manufacturers' data books for additional information.

IGURE 3.1A • 8051 Block Diagram

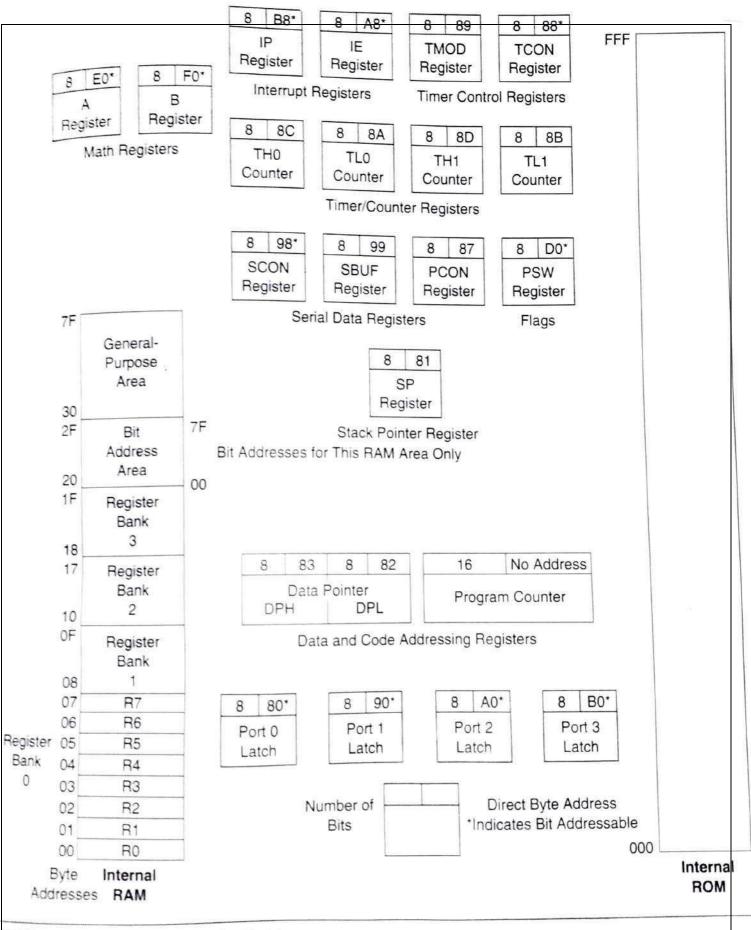

The programming model of the 8051 in Figure 3.1b shows the 8051 as a collection of 8- and 16-bit registers and 8-bit memory locations. These registers and memory locations can be made to operate using the software instructions that are incorporated as part of the design. The program instructions have to do with the control of the registers and digital data paths that are physically con-

FIGURE 3.1B . 8051 Programming Model

tained inside the 8051, as well as memory locations that are physically located

side the 8051. The model is complicated by the number of special-purpose registers that outside the 8051. The model is complicated by the function of the first-time viewer: return to the must be present to make a microcomputer a microcontroller. A cursory inspective viewer: return to the second for the first-time viewer: return to the second se must be present to make a million of the first-time viewer; return to the model tion of the model is recommended for the first-time of the text as needed while progressing through the remainder of the text.

Most of the registers have a specific function; those that do occupy an indi-Most of the registers have a openance as A or THO or PC. Others, which are vidual block with a symbolic name, such as A or THO or PC. Others, which are vidual block with a symbolic mane, each other, are grouped in a larger block, such generally indistinguishable from each other, are grouped in a larger block, such as internal ROM or RAM memory.

Each register, with the exception of the program counter, has an internal 1-byte address assigned to it. Some registers (marked with an asterisk\* in Fig. ure 3.1b) are both byte and bit addressable. That is, the entire byte of data at such register addresses may be read or altered, or individual bits may be read or altered. Software instructions are generally able to specify a register by its ad. dress, its symbolic name, or both.

A pinout of the 8051 packaged in a 40-pin DIP is shown in Figure 3.2 with the full and abbreviated names of the signals for each pin. It is important to note that many of the pins are used for more than one function (the alternate functions are shown in parentheses in Figure 3.2). Not all of the possible 8051 features may be used at the same time.

Programming instructions or physical pin connections determine the use of any multifunction pins. For example, port 3 bit 0 (abbreviated P3.0) may be used as a general-purpose I/O pin, or as an input (RXD) to SBUF, the serial data receiver register. The system designer decides which of these two functions is to be used and designs the hardware and software affecting that pin accordingly.

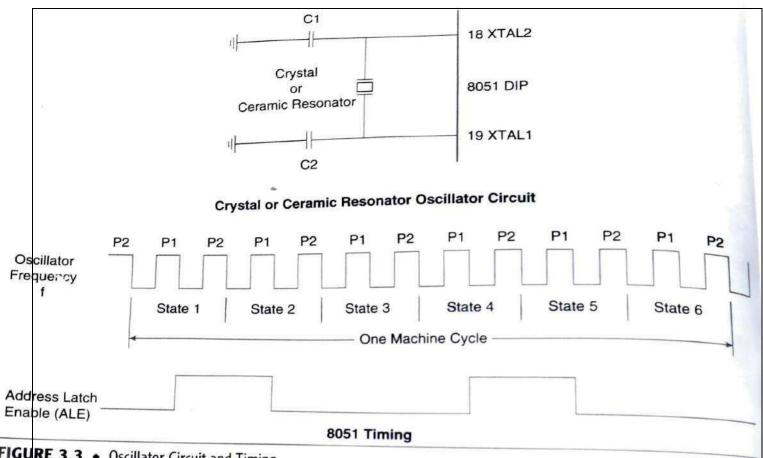

# The 8051 Oscillator and Clock

The heart of the 8051 is the circuitry that generates the clock pulses by which all internal operations are synchronized. Pins XTAL1 and XTAL2 are provided for connecting a resonant network to form an oscillator. Typically, a quartz crystal and capacitors are employed, as shown in Figure 3.3. The crystal frequency is the basic internal clock frequency of the microcontroller. The manufacturers make available 8051 designs that can run at specified maximum and minimum frequencies, typically 1 megahertz to 16 megahertz. Minimum frequencies imply that some internal memories are dynamic and must always op-

erate above a minimum frequency or data will be lost. Serial data communication needs often dictate the frequency of the oscillator because of the requirement that internal counters must divide the basic clock rate to yield standard communication bit per second (baud) rates. If the basic clock frequency is not divisible without a remainder, then the resulting

| Port 1 Bit 0                    | 1 P1.0        | Vcc 40       | + 5V                                          |

|---------------------------------|---------------|--------------|-----------------------------------------------|

| Port 1 Bit 1                    | 2 P1.1        | (AD0)P0.0 39 | Port 0 Bit 0                                  |

| Port 1 Bit 2                    | 3 P1.2        | (AD1)P0.1 38 | (Address/Data 0)<br>Port 0 Bit 1              |

| Port 1 Bit 3                    | 4 P1.3        | (AD2)P0.2 37 | (Address/Data 1)<br>Port 0 Bit 2              |

| Port 1 Bit 4                    | 5 P1.4        | (AD3)P0.3 36 | (Address/Data 2)<br>Port 0 Bit 3              |

| Port 1 Bit 5                    | 6 P1.5        | (AD4)P0.4 35 | (Address/Data 3)<br>Port 0 Bit 4              |

| Port 1 Bit 6                    | 7 P1.6        | (AD5)P0.5 34 | (Address/Data 4)<br>Port 0 Bit 5              |

| Port 1 Bit 7                    | 8 P1.7        | (AD6)P0.6 33 | (Address/Data 5)<br>Port 0 Bit 6              |

| Reset Input                     | 9 RST         | (AD7)P0.7 32 | (Address/Data 6)<br>Port 0 Bit 7              |

| Port 3 Bit 0                    | 10 P3.0(RXD)  | (Vpp)/EA 31  | (Address/Data 7)<br>External Enable           |

| (Receive Data)                  |               |              | (EPROM Programming Voltage)                   |

| Port 3 Bit 1<br>(XMIT Data)     | 11 P3.1(TXD)  | (PROG)ALE 30 | Address Latch Enable<br>(EPROM Program Pulse) |

| Port 3 Bit 2<br>(Interrupt 0)   | 12 P3.2(INT0) | PSEN 29      | Program Store Enable                          |

| Port 3 Bit 3<br>(Interrupt 1)   | 13 P3.3(INT1) | (A15)P2.7 28 | Port 2 Bit 7<br>(Address 15)                  |

| Port 3 Bit 4<br>(Timer 0 Input) | 14 P3.4(T0)   | (A14)P2.6 27 | Port 2 Bit 6<br>(Address 14)                  |

| Port 3 Bit 5<br>(Timer 1 Input) | 15 P3.5(T1)   | (A13)P2.5 26 | Port 2 Bit 5<br>(Address 13)                  |

| Port 3 Bit 6<br>(Write Strobe)  | 16 P3.6(WR)   | (A12)P2.4 25 | Port 2 Bit 4<br>(Address 12)                  |

| Port 3 Bit 7<br>(Read Strobe)   | 17 P3.7(RD)   | (A11)P2.3 24 | Port 2 Bit 3<br>(Address 11)                  |

| Crystal Input 2                 |               | (A10)P2.2 23 | Port 2 Bit 2<br>(Address 10)                  |

| Crystal Input 1                 | 19 XTAL1      | (A9)P2.1 22  | Port 2 Bit 1<br>(Address 9)                   |

| Ground                          | 20 Vss        | (A8)P2.0 21  | Port 2 Bit 0<br>(Address 8)                   |

|                                 |               |              |                                               |

Note: Alternate functions are shown below the port name (in parentheses). Pin numbers and pin names are shown inside the DIP package.

FIGURE 3.3 • Oscillator Circuit and Timing

Ceramic resonators may be used as a low-cost alternative to crystal resonators. However, decreases in frequency stability and accuracy make the ce ramic resonator a poor choice if high-speed serial data communication with other systems, or critical timing, is to be done.

The oscillator formed by the crystal, capacitors, and an on-chip inverter

generates a pulse train at the frequency of the crystal, as shown in Figure 3.3 The clock frequency, f, establishes the smallest interval of time within the microcontroller, called the pulse, P, time. The smallest interval of time to accomplish any simple instruction, or part of a complex instruction, however, s the machine cycle. The machine cycle is itself made up of six states. A state is the basic time interval for discrete operations of the microcontroller such as fetching an opcode byte, decoding an opcode, executing an opcode, or writing a data byte. Two oscillator pulses define each state.

Program instructions may require one, two, or four machine cycles to be executed, depending on the type of instruction. Instructions are fetched and executed by the microcontroller automatically, beginning with the instruction

crystal, although seemingly an odd value, yields a cycle frequency of 921.6 kilohertz, which can be divided evenly by the standard communication baud rates of 19200, 9600, 4800, 2400, 1200, and 300 hertz.

Note, in Figure 3.3, there are two ALE pulses per machine cycle. The ALE pulse, which is primarily used as a timing pulse for external memory access, indicates when every instruction byte is fetched. Two bytes of a single instruction may thus be fetched, and executed, in one machine cycle. Single-byte instructions are not executed in a half cycle, however. Single-byte instructions "throw-away" the second byte (which is the first byte of the next instruction). The next instruction is then fetched in the following cycle.

## Program Counter and Data Pointer

The 8051 contains two 16-bit registers: the program counter (PC) and the data pointer (DPTR). Each is used to hold the address of a byte in memory.

Program instruction bytes are fetched from locations in memory that are addressed by the PC. Program ROM may be on the chip at addresses 0000h to 0FFFh, external to the chip for addresses that exceed 0FFFh, or totally external for all addresses from 0000h to FFFFh. The PC is automatically incremented after every instruction byte is fetched and may also be altered by certain instructions. The PC is the only register that does not have an internal address.

The DPTR register is made up of two 8-bit registers, named DPH and DPL, which are used to furnish memory addresses for internal and external code access and external data access. The DPTR is under the control of program instructions and can be specified by its 16-bit name, DPTR, or by each individual byte name, DPH and DPL. DPTR does not have a single internal address; DPH and DPL are each assigned an address.

## A and B CPU Registers

The 8051 contains 34 general-purpose, or working, registers. Two of these, registers A and B, hold results of many instructions, particularly math and logical

operations, of the 8051 central processing unit (CPU). The other 32 are arranged as part of internal RAM in four banks, BO - B3, of eight registers and comprise the mathematical core.

The A (accumulator) register is the most versatile of the two CPU registers and is used for many operations, including addition, subtraction, integer mul. tiplication and division, and Boolean bit manipulations. The A register is also used for all data transfers between the 8051 and any external memory. The Bregister is used with the A register for multiplication and division operations and has no other function other than as a location where data may be stored.

### Flags and the Program Status Word (PSW)

Flags are 1-bit registers provided to store the results of certain program instructions. Other instructions can test the condition of the flags and make decisions based on the flag states. In order that the flags may be conveniently addressed, they are grouped inside the program status word (PSW) and the power control (PCON) registers.

The 8051 has four math flags that respond automatically to the outcomes of math operations and three general-purpose user flags that can be set to 1 or cleared to 0 by the programmer as desired. The math flags include Carry (C), Auxiliary Carry (AC), Overflow (OV), and Parity (P). User flags are named F0, GF0, and GF1; they are general-purpose flags that may be used by the programmer to record some event in the program. Note that all of the flags can be set and cleared by the programmer at will. The math flags, however, are also affected by math operations.

The program status word is shown in Figure 3.4. The PSW contains the math flags, user program flag F0, and the register select bits that identify which of the four general-purpose register banks is currently in use by the program. The remaining two user flags, GF0 and GF1, are stored in PCON, which is shown in Figure 3.13.

Detailed descriptions of the math flag operations will be discussed in chapters that cover the opcodes that affect the flags. The user flags can be set or cleared using data move instructions covered in Chapter 5.

# Internal Memory

A functioning computer must have memory for program code bytes, commonly in ROM, and RAM memory for variable data that can be altered as the program runs. The 8051 has internal RAM and ROM memory for these functions. Addi-

tional memory can be added externally using suitable circuits. Unlike microcontrollers with Von Neumann architectures, which can use a single memory address for either program code or data, but not for both, the 8051

has a Harvard architecture, which uses the same address, in different memo-

|             | 7<br>C1        | PO RS1 RS0 V - P                                                                                                                       |

|-------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------|

| The l       | Program Sta    | atus Word (PSW) Special Function Register                                                                                              |

| Bit         | Symbol         | Function                                                                                                                               |

| 7<br>6<br>5 | CY<br>AC<br>F0 | Carry flag; used in arithmetic, jump, rotate, and Boolean instructions<br>Auxiliary Carry flag; used for BCD arithmetic<br>User flag 0 |

|             | RS1            | Register bank select bit 1                                                                                                             |

| 4 3         | RS0            | Register bank select bit 0RS1RS000Select register bank 001Select register bank 110Select register bank 211Select register bank 3       |

| 2           | OV             | Overflow flag; used in arithmetic instructions                                                                                         |

| 1           | _              | Reserved for future use                                                                                                                |

| 0           | Ρ              | Parity flag; shows parity of register A: $1 = \text{Odd Parity}$<br>Bit addressable as PSW.0 to PSW.7                                  |

FIGURE 3.4 + PSW Program Status Word Register

ries, for code and data. Internal circuitry accesses the correct memory based on the nature of the operation in progress.

## Internal RAM

The 128-byte internal RAM, which is shown generally in Figure 3.1 and in detail in Figure 3.5, is organized into three distinct areas:

- 1. Thirty-two bytes from address 00h to 1Fh that make up 32 working registers organized as four banks of eight registers each. The four register banks are numbered 0 to 3 and are made up of eight registers named R0 to R7. Each register can be addressed by name (when its bank is selected) or by its RAM address. Thus R0 of bank 3 is R0 (if bank 3 is currently selected) or address 18h (whether bank 3 is selected or not). Bits RS0 and RS1 in the PSW determine which bank of registers is currently in use at any time when the program is running. Register banks not selected can be used as general-purpose RAM. Bank 0 is selected on reset.

- A bit-addressable area of 16 bytes occupies RAM byte addresses 20h to 2Fh, forming a total of 128 addressable bits. An addressable bit may be

|        |                  | 5                                                                                                              | 41     |      |           | Byte<br>Addres | S         |

|--------|------------------|----------------------------------------------------------------------------------------------------------------|--------|------|-----------|----------------|-----------|

|        | By<br>Add        | rte<br>ress                                                                                                    |        |      | 10        | 7F             |           |

|        |                  | = R7                                                                                                           |        |      |           |                |           |

|        | 1E               | the second s |        |      |           |                |           |

|        | 10               |                                                                                                                |        |      |           |                |           |

| Bank 3 | 1C               | R4                                                                                                             |        |      |           |                |           |

| Bar    | 1B               | R3                                                                                                             |        |      |           |                |           |

|        | 1A               | R2                                                                                                             |        |      |           |                |           |

|        | 19               | R1                                                                                                             |        |      |           |                | 19        |

|        | 18               | R0                                                                                                             |        |      |           |                |           |

|        | 17               | R7                                                                                                             |        |      |           |                |           |

|        | 16               | R6                                                                                                             |        |      |           |                |           |

| 2      | 15               | R5                                                                                                             |        |      |           | 0.             |           |

| Bank 2 | 14               | R4                                                                                                             |        |      |           |                |           |

| Ba     | 13               | R3                                                                                                             |        |      |           |                |           |

|        | 12               | R2                                                                                                             |        |      |           |                |           |

|        | 11               | R1                                                                                                             | Byte   |      | Bit       |                |           |

|        | $-\frac{10}{05}$ | R0                                                                                                             | Addres | ss A | ddresses  |                |           |

|        | 0F               | R7                                                                                                             | 2F     | 7F   | 78        |                | <u>N.</u> |

|        | 0E               | R6                                                                                                             | 2E     | 77   | 70        |                |           |

| -      |                  | R5                                                                                                             | 2D     | 6F   | 68        |                |           |

| Bank 1 | 0C               | R4                                                                                                             | 2C     | 67   | 60        | ſ              |           |

| ä      | 0B               | R3                                                                                                             | 2B     | 5F   |           |                |           |

|        | 0A               | R2                                                                                                             | 2A     | 57   | 58        |                |           |

|        | 09               | R1                                                                                                             | 29     | 4F   | 50        |                |           |

|        | 08               | RO                                                                                                             | 28     | 47   | 48        |                |           |

|        | 07               | R7                                                                                                             | 27     |      | 40        |                |           |

|        | 06               | R6                                                                                                             |        | 3F   | 38        |                |           |

| 0      | 05               | R5                                                                                                             | 26     | 37   | 30        |                |           |

| Bank 0 | 04               | R4                                                                                                             | 25     | 2F   | 28        |                |           |

| Ba     | 03               | R3                                                                                                             | 24     | .27  | 20        |                |           |

|        | 02               | R2                                                                                                             | 23     | 1F   | 18        |                |           |

|        | 01               | R1                                                                                                             | 22     | 17   | 10        |                |           |

|        | 00               | R0                                                                                                             | 21     | 0F   | 08        |                |           |

|        | ·                | 110                                                                                                            | 20     | 07   |           |                |           |

|        |                  | \A/                                                                                                            |        | 7 🗸  | 00        | 30             |           |

|        |                  | Working<br>Registers                                                                                           |        |      | dressable |                |           |

specified by its bit address of 00h to 7Fh, or 8 bits may form any byte address from 20h to 2Fh. Thus, for example, bit address 4Fh is also bit 7 of byte address 29h. Addressable bits are useful when the program need only remember a binary event (switch on, light off, etc.). Internal RAM is in short supply as it is, so why use a byte when a bit will do?

3. A general-purpose RAM area above the bit area, from 30h to 7Fh, addressable as bytes.

## The Stack and the Stack Pointer

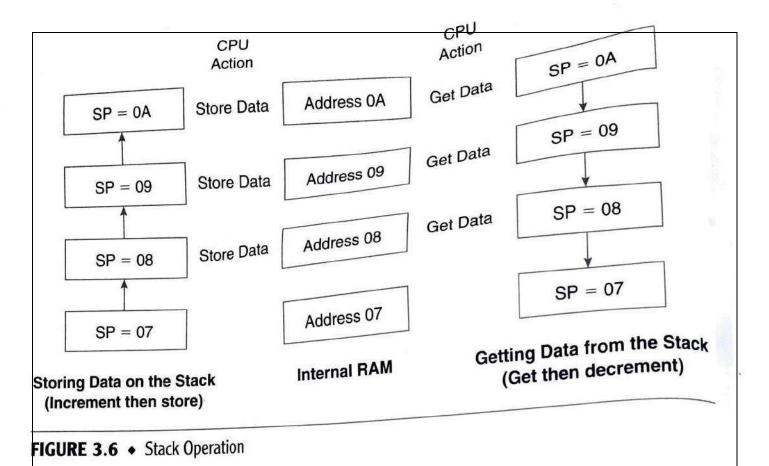

The stack refers to an area of internal RAM that is used in conjunction with certain opcodes to store and retrieve data quickly. The 8-bit Stack Pointer (SP) register is used by the 8051 to hold an internal RAM address that is called the top of the stack. The address held in the SP register is the location in internal RAM where the last byte of data was stored by a stack operation.

When data is to be placed on the stack, the SP increments before storing data on the stack so that the stack grows up as data is stored. As data is retrieved from the stack, the byte is read from the stack, and then the SP decrements to point to the next available byte of stored data.

Operation of the stack and the SP is shown in Figure 3.6. The SP is set to 07h when the 8051 is reset and can be changed to any internal RAM address by the programmer, using a data move command from Chapter 5.

The stack is limited in height to the size of the internal RAM. The stack has the potential (if the programmer is not careful to limit its growth) to overwrite valuable data in the register banks, bit-addressable RAM, and scratch-pad RAM areas. The programmer is responsible for making sure the stack does not grow beyond predefined bounds!

The stack is normally placed high in internal RAM, by an appropriate choice of the number placed in the SP register, to avoid conflict with the register, bit, and scratch-pad internal RAM areas.

## Special Function Registers

The 8051 operations that do not use the internal 128-byte RAM addresses from 00h to 7Fh are done by a group of specific internal registers, each called a Special-Function register (SFR), which may be addressed much like internal RAM, using addresses from 80h to FFh.

Some SFRs (marked with an asterisk\* in Figure 3.1b) are also bit addressable, as is the case for the bit area of RAM. This feature allows the programmer to change only what needs to be altered, leaving the remaining bits in that SFR unchanged.

Not all of the addresses from 80h to FFh are used for SFRs, and attempting to use an address that is not defined, or *empty*, results in unpredictable results.

In Figure 3.1b, the SFR addresses are shown in the upper right corner of each block. The SFR names and equivalent internal RAM addresses are given in Table 3.1. Note that the PC is not part of the SFR and has no internal RAM address. See also Appendix F.

SFRs are named in certain opcodes by their functional names, such as A or THO, and are referenced by other opcodes by their addresses, such as OEOh or 8Ch. Note that *any* address used in the program *must* start with a number; thus address E0h for the A SFR begins with 0. Failure to use this number convention will result in an assembler error when the program is assembled.

# **nternal ROM**

The 8051 is organized so that data memory and program code memory can be n two entirely different physical memory entities. Each has the same address ranges.

The structure of the internal RAM has been discussed previously. A corresponding block of internal program code, contained in an internal ROM, occupies code address space 0000h to 0FFFh. The PC is ordinarily used to address ban OFFFh which addresses 0000h to FFFFh. Program addresses higher han OFFFh, which exceed the internal ROM capacity, will cause the 8051 to automatically fetch code bytes from external program memory. Code bytes can

| TABLE 3. | 1                          |                   |

|----------|----------------------------|-------------------|

| Name     | Function Internal I        | RAM Address (HEX) |

| А        | Accumulator                | 0E0               |

| B        | Arithmetic                 | 0F0               |

| DPH      | Addressing external memory | 83                |

| DPL      | Addressing external memory | 82                |

| IE       | Interrupt enable control   | 0A8               |

| IP       | Interrupt priority         | 0B8               |

| P0       | Input/output port latch    | 80                |

| P1       | Input/output port latch    | 90                |

| P2       | Input/output port latch    | AO                |

| P3       | Input/output port latch    | 0B0               |

| PCON     | Power control              | 87                |

| PSW      | Program status word        | 0D0               |

| SCON     | Serial port control        | 98                |

| BUF      | Serial port data buffer    | 99                |

| P        | Stack pointer              | 81                |

| MOD      | Timer/counter mode control | 89                |

| CON      | Timer/counter control      | 88                |

| LO       | Timer 0 low byte           | 8A                |

| НО       | Timer 0 high byte          | 8C                |

| _1       | Timer 1 low byte           | 8B                |

| -11      | Timer 1 high byte          | 8D                |

also be fetched exclusively from an external memory, addresses 0000h to FFFFh, by connecting the external access pin (EA pin 31 on the DIP) to ground. The PC does not care where the code is; the circuit designer decides whether the code is found totally in internal ROM, totally in external ROM, or in a combination of internal and external ROM.

|    | 1. Internal RAM                                                                                |                                                                                             |

|----|------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

|    | <ol> <li>Internal special-fund</li> <li>External RAM</li> <li>Internal and external</li> </ol> | 1 ROM                                                                                       |

|    | Finally, the followi<br>1. MOV<br>2. MOVX<br>3. MOVC<br>4. PUSH and POP<br>5. XCH              | ng five types of opcodes are used to move data:                                             |

| 13 |                                                                                                | ◆ COMMENT ◆                                                                                 |

|    | All of the following opco<br>may be assembled and<br>each example:                             | d debugged by adding these code lines to the code found in                                  |

|    | org 0000h<br>loop:<br>(insert code here<br>sjmp loop                                           | ; start code at 0000h<br>; a label to jump to (Chapter 8)<br>e)<br>; jump back to beginning |

|    | end                                                                                            | ; end the program                                                                           |

# 5.1 Addressing Modes

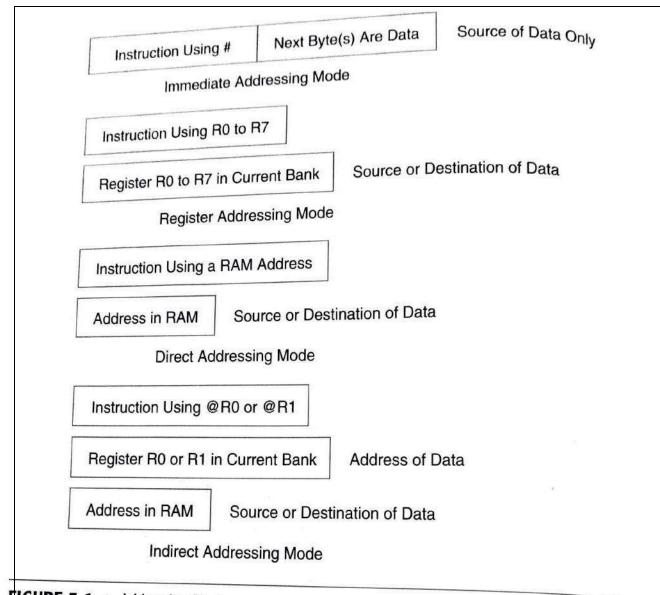

The way the data sources or destination addresses are specified in the mnemonic that moves that data determines the addressing mode. Figure 5.1 diagrams the four addressing modes: immediate, register, direct, and indirect.

## Immediate Addressing Mode

The simplest way to get data to a destination is to make the source of the data part of the opcode. The data source is then immediately available as part of the instruction itself.

When the 8051 executes an immediate data move, the program counter is automatically incremented to point to the byte(s) following the opcode byte in the program memory. Whatever data is found there is copied to the destination address.

#### CHAPIERS

The mnemonic for immediate data is the pound sign (#). Occasionally, in the rush to meet a deadline, we might forget to use the # for immediate data. The resulting opcode is often a legal command that is assembled with no objections by the assembler. This omission groups in the second s

tions by the assembler. This omission guarantees that the rush will continue. Three mnemonics can copy immediate numbers from the opcode into registers R0-R7 (of the currently selected register bank), A, and DPTR:

|                                      | man und DI IK:                                                                                                                                                                                    |

|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MOV Rr,#n<br>MOV A,#n<br>MOV DDTD :: | Operation<br>Copy the 8-bit number n into register Rr (of the current register bank)<br>Copy the 8-bit number n into the Accumulator register<br>Copy the 16-bit number nn into the DPTR register |

| Immediate add                        | ·······································                                                                                                                                                           |

the currently selected register bank, register A, and register DPTR, are shown in

| Mnemonic        | Operation                                              |

|-----------------|--------------------------------------------------------|

| MOV R0,#00h     | Put the immediate 8-bit number 00h in register R0      |

| MOV R1,#01h     | Put the immediate 8-bit number 01h in register R1      |

| MOV R4,#04h     | Put the immediate 8-bit number 04h in register R4      |

| MOV R7,#07h     | Put the immediate 8-bit number 07 in register R7       |

| MOV A,#0AAh     | Put the immediate 8-bit number AAh in register A       |

| MOV DPTR,#1234h | Put the immediate 16-bit number 1234h in register DPTR |

## **Register Addressing Mode**

Certain register names may be used as part of the opcode mnemonic as sources or destinations of data. Registers A, DPTR, and R0 to R7 may be named as part of the opcode mnemonic. Other registers in the 8051 may be addressed using the direct addressing mode. Some assemblers can equate many of the direct addresses to the register name (as is the case with the assembler discussed in this book) so that register names may be used in lieu of register addresses. Remember that the registers used in the opcode as R0 to R7 are the ones that are *currently* chosen by the bank-select bits, RS0 and RS1 in the PSW.

Register-to-register moves are as follows:

| Mnemonic  | Operation                                |

|-----------|------------------------------------------|

| MOV A, Rr | Copy data from register Rr to register A |

| MOV Rr,A  | Copy data from register A to register Rr |

A data MOV does not alter the contents of the data source address. A *copy* of the data is made from the source and moved to the destination address. The contents of the destination address are replaced by the source address contents. The following list shows examples of MOV opcodes with immediate and register addressing modes:

| Mnemonic         | Operation                                          |

|------------------|----------------------------------------------------|

| MOV A,#0F1h      | Move the immediate data byte F1h to the A register |

| MOV A, R0        | Copy the data in register R0 to register A         |

| MOV DPTR,#0ABCDh | Move the immediate data bytes ABCDh to the DPTR    |

| MOV R5,A         | Copy the data in register A to register R5         |

| MOV R3,#1Ch      | Move the immediate data byte 1Ch to register R3    |

### ♦ CAUTION ♦

- It is impossible to have immediate data as a destination.

- All numbers must start with a decimal number (0 − 9), or the assembler assumes the number is a label.

- Register-to-register moves using the register addressing mode occur between registers A and R0 to R7.

# Direct Addressing Mode

All 128 bytes of internal RAM and the SFRs may be addressed directly  $u_{\delta}$ . All 128 bytes of internal RAM and the of its may location and each special ing the single-byte address assigned to each RAM location and each special. function register. See Appendix F for an overall SFR/memory map.

ction register. See Appendix F for an overall or of the address each byte. The Internal RAM uses addresses from 00h to 7Fh to address each byte. The SFR addresses exist from 80h to FFh at the locations shown in Table 5.1.

### CAUTION ◆

- Note that there are "gaps" in the addresses of the SFRs; the addresses are not in order.

- Note the use of a leading 0 for all numbers that begin with an alphabetic (alpha) character.

RAM addresses 00 to 1Fh are also the locations assigned to the four banks of eight working registers, R0 to R7. This assignment means that R2 of register

| TABLE 5 | .1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SFR     | Address (hex)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| A       | 0E0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| B       | OFO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| DPL     | 82                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| DPH     | 83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| IE      | 0A8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| IP      | 0B8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| PO      | 80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| P1      | 90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| P2      | 0A0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| P3      | 0B0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| PCON    | 87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |